8位并行二进制加法器

8位并行二进制全加器的深度解析

在计算机科学与技术的广阔领域中,加法器作为实现二进制数相加运算的基本单元电路,扮演着至关重要的角色。而8位并行二进制全加器,则是这一基础概念的延伸与扩展,它不仅在数字逻辑设计中占据了核心地位,还是理解高级计算机体系结构不可或缺的基石。本文将从8位并行二进制全加器的基本概念、设计原理、实现方法以及应用场景等多个维度,对其进行全面而深入的解析。

一、基本概念

8位并行二进制全加器,顾名思义,是一种能够同时处理8位二进制数相加的逻辑电路。在二进制体系中,每一位的加法运算都是独立的,但进位信号需要在相邻位之间传递。因此,全加器相较于只能处理一位加法的半加器,额外考虑了来自低位的进位输入。在8位并行二进制全加器中,这8个全加器是并行工作的,每一位的加法运算同时进行,大大提高了计算效率。

二、设计原理

2.1 半加器与全加器的基础

在深入探讨8位并行二进制全加器之前,有必要先回顾一下半加器和全加器的基础知识。半加器仅处理两个二进制数的相加,不考虑进位,因此只需一个异或门和一个与门即可实现。而异或门用于产生和,与门则用于产生进位。

全加器则是在半加器的基础上增加了对进位的处理。它有三个输入:两个加数和一个来自低位的进位输入。为了实现全加功能,通常需要使用两个半加器和一个或门。其中一个半加器处理两个加数的和,另一个半加器则处理其中一个加数与低位进位的和。两个半加器的进位输出通过或门合并,形成全加器的进位输出。

2.2 8位并行二进制全加器的构建

基于全加器的基础,8位并行二进制全加器由8个全加器级联而成。每个全加器的进位输出连接到下一个全加器的进位输入,形成一个串行进位链。这种设计确保了每一位的加法运算都能同时开始,但进位信号会按照从低位到高位的顺序传递。

三、实现方法

3.1 硬件实现

在硬件层面,8位并行二进制全加器可以通过集成电路(IC)实现。例如,使用74LS283这样的四位二进制加法器IC,通过两个74LS283的串联,可以构建一个八位二进制加法器。当然,这种实现方式需要考虑到进位修正的问题,因为74LS283是按四位二进制数进行运算的,即逢十六进一,而二进制加法是逢二进一,十进制加法则是逢十进一。在处理BCD码(二进制编码的十进制数)相加时,还需要额外的逻辑电路来修正进位。

3.2 软件仿真

随着计算机仿真技术的发展,软件仿真成为了设计和验证数字逻辑电路的重要工具。在Logisim这样的数字逻辑仿真软件中,可以轻松地设计和仿真8位并行二进制全加器。通过拖拽逻辑门、全加器等组件,连接成电路图,然后输入测试信号进行仿真,可以直观地观察到加法器的运算过程和结果。这种方法不仅降低了硬件成本,还大大提高了设计效率和灵活性。

四、应用场景

8位并行二进制全加器在计算机系统和数字电子设备中有着广泛的应用。以下是一些典型的应用场景:

4.1 微处理器与微控制器

在微处理器和微控制器中,8位并行二进制全加器是算术逻辑单元(ALU)的重要组成部分。ALU负责执行算术和逻辑运算,而加法运算则是其中最基础也最重要的一种。因此,8位并行二进制全加器的性能直接影响着微处理器和微控制器的计算能力和效率。

4.2 数字信号处理

在数字信号处理领域,8位并行二进制全加器被广泛应用于滤波、变换、编码等算法中。这些算法通常需要对大量的数字信号进行加法运算,而8位并行二进制全加器的高效并行处理能力能够显著提升算法的执行速度。

4.3 通信系统

在通信系统中,8位并行二进制全加器也发挥着重要作用。例如,在差错控制编码中,加法运算被用于生成校验码和检测错误。8位并行二进制全加器能够快速准确地完成这些运算,从而确保通信的可靠性和稳定性。

五、性能优化与挑战

尽管8位并行二进制全加器在许多应用场景中都表现出色,但其性能优化仍面临一些挑战。例如,进位传递的延迟是限制加法器速度的关键因素之一。为了降低这种延迟,可以采用超前进位加法器(Carry-Lookahead Adder)等更复杂的电路结构。然而,这些结构往往会增加电路的复杂性和功耗。

此外,随着集成电路工艺的不断进步和计算机系统对性能要求的不断提高,如何在保持低功耗的同时提高加法器的运算速度和精度,成为了当前研究的热点和难点。

六、结语

综上所述,8位并行二进制全加器作为数字逻辑设计中的重要组件,在计算机科学与技术领域发挥着举足轻重的作用。通过深入理解其设计原理和实现方法,我们可以更好地利用这一工具来构建高效、可靠的数字电子系统。同时,面对性能优化和功耗降低等挑战,我们也需不断探索新的技术和方法,以推动数字逻辑设计领域的持续进步和发展。

- 上一篇: 解锁玫瑰小镇花盆升级秘籍!

- 下一篇: 十二生肖中哪个动物会落井下石?

-

两位数加一位数进位加法的全面解析资讯攻略11-07

两位数加一位数进位加法的全面解析资讯攻略11-07 -

《万王之王3》巫术师技能点怎么加?资讯攻略12-10

《万王之王3》巫术师技能点怎么加?资讯攻略12-10 -

100 Doors 3图文攻略前10关怎么过?资讯攻略11-28

100 Doors 3图文攻略前10关怎么过?资讯攻略11-28 -

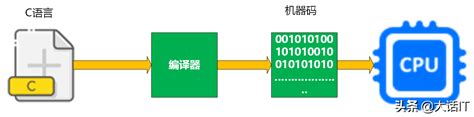

揭秘:机器码背后的奥秘与运作原理资讯攻略04-09

揭秘:机器码背后的奥秘与运作原理资讯攻略04-09 -

显存位宽的重要性及作用解析资讯攻略12-02

显存位宽的重要性及作用解析资讯攻略12-02 -

Excel技巧:轻松实现双窗口并行操作资讯攻略01-18

Excel技巧:轻松实现双窗口并行操作资讯攻略01-18